Полная версия

Цифровые устройства. Учебник для колледжей

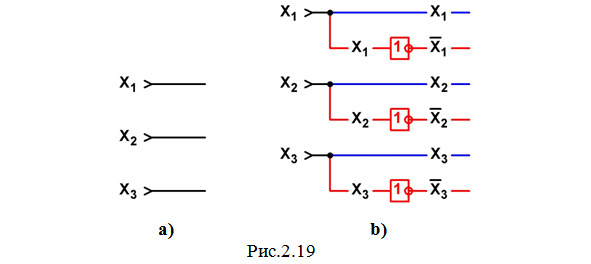

а) Чертим все три входа Х1, Х2 и Х3 (рис.2.19а).

В дальнейшем на каждом следующем этапе все новые элементы, которые будут включаться в схему, показываются красным цветом.

b) Смотрим на МДНФ и видим, что операции НЕ должны выполняться в данном случае со всеми тремя переменными, т.к. в этом выражении имеются величины X1′, X2′ и X3′. Поэтому на всех трех входах ставим элементы НЕ (рис.2.19b.). Входы элементов подключаем ко входам схемы X1, X2 и X3, на выходах будут формироваться инверсные значения входных сигналов X1′, X2′ и X3′.

Сразу же нужно учесть еще один момент: снова смотрим на МДНФ и обнаруживаем, что наряду с инверсными значениями всех (еще раз повторяем: в данном случае всех) сигналов X1′, X2′ и X3′ нам потребуются и их прямые значения, поэтому выводим в схему и провода, показанные синим цветом.

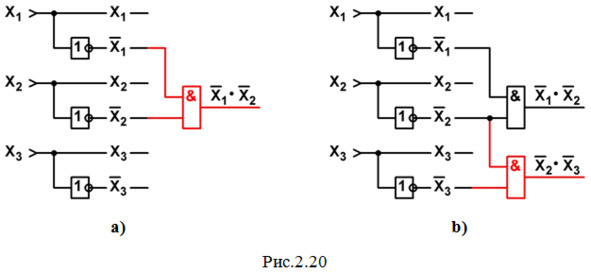

c) Теперь переходим к выполнению операций логического умножения. Начнем с операции X1′·X2′ (смотрите МДНФ). Чертим элемент 2И; на один его вход подаем X1′, на другой – X2′; на выходе получаем результат умножения: X1′·X2′. К настоящему моменту мы будем иметь схему, изображенную на рис.2.20a.

d) Реализуем следующую операцию умножения: X2′·X3′ (смотрите МДНФ). Чертим еще один элемент 2И; на один его вход подаем X2′, на другой – X3′; на выходе получаем результат: X2′·X3′. Теперь схема примет вид рис.2.20b.

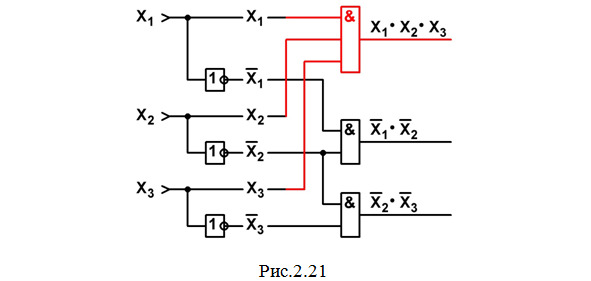

e) В последнем многочлене МДНФ X1·X2·X3 нужно выполнить операцию умножения с тремя сигналами, поэтому чертим элемент 3И. На один его вход подаем X1, на второй – X2 и на третий – X3; на выходе получим результат: X1·X2·X3. И схема теперь будет иметь вид рис.2.21.

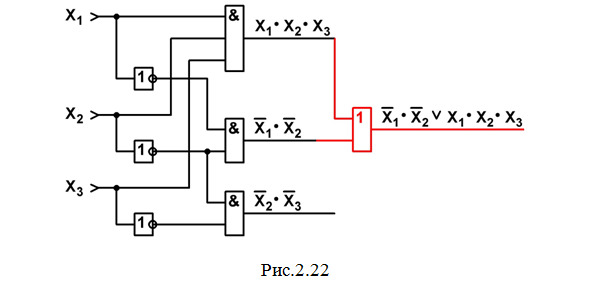

f) Переходим к реализации операций логического сложения полученных многочленов: X1′·X2′, X2′·X3′ и X1·X2·X3 с помощью двух элементов 2ИЛИ. Как известно, при перемене мест слагаемых сумма не меняется; поэтому совершенно безразлично, в какой последовательности мы будем выполнять эти операции. Начнем с логического сложения многочленов X1′·X2′ и X1·X2·X3. Начертим элемент 2ИЛИ; на один его вход подадим X1′·X2′, на другой – X1·X2·X3; на выходе получим результат сложения: X1′·X2′ \/ X1·X2·X3. Теперь схема будет выглядеть так, как на рис.2.22.

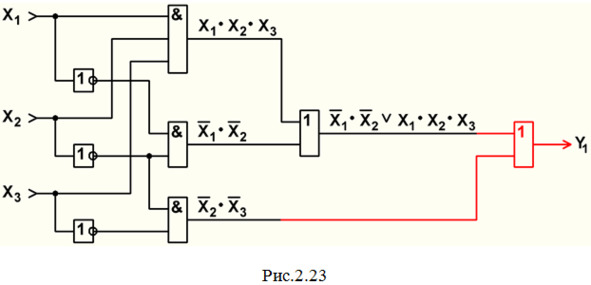

g) Остается лишь к величине (X1′·X2′ \/ X1·X2·X3) прибавить многочлен X2′·X3′. Чертим последний элемент – элемент 2ИЛИ; на один его вход подаем (X1′·X2′ \/ X1·X2·X3), на другой – X2′·X3′; на выходе этого элемента (так как он последний) получаем значение выходной функции Y1. И схема примет вид рис.2.23.

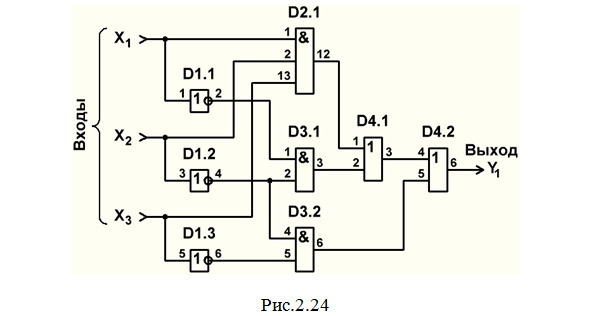

Теперь уберем вспомогательные надписи, укажем входы и выход, проставим позиционное обозначение всех элементов схемы с соответствующей нумерацией.

Микросхемы на чертежах обозначаются буквой D (от английского device – устройство) с соответствующим номером, например: D1, D2, D3 и т. д. Допускается в позиционное обозначение добавлять вторую букву: DА (A – analogy) – аналоговая микросхема, DD (D – digital) – цифровая микросхема; но это делается обычно тогда, когда в схеме присутствуют микросхемы обоих типов. А так как у нас в дальнейшем на чертежах будут только цифровые микросхемы, то мы вторую букву ставить не будем. Нумерацию микросхем и любых других элементов следует по возможности выполнять сверху вниз «колонками», начиная с левой стороны схемы.

На нашем чертеже в первой колонке стоят элементы НЕ из микросхемы КР1533ЛН1, которую поэтому следует обозначить D1. Но как обозначить отдельные элементы этой ИМС? Существует следующее правило: если микросхема содержит несколько элементов, то они обозначаются с двойной нумерацией через точку, причем первая цифра указывает номер микросхемы, а вторая – номер элемента в этой микросхеме. В данном случае первый элемент НЕ из микросхемы КР1533ЛН1 (напомним, что ее мы обозначили D1) нужно обозначить D1.1, второй элемент – D1.2, третий – D1.3.

Во второй колонке первым стоит элемент 3И из микросхемы КР1533ЛИ3, поэтому ее мы обозначим следующим по порядку номером D2. В указанной микросхеме используется один элемент 3И, который будет иметь обозначение D2.1.

В этой же второй колонке далее стоят два элемент 2И из микросхемы КР1533ЛИ1, их мы обозначим D3.1 и D3.2.

Последними в схеме стоят два элемента 2ИЛИ из микросхемы КР1533ЛЛ1, их нужно обозначить D4.1 и D4.2.

Кроме этого, у всех элементов схемы следует указать нумерацию их выводов в корпусе микросхем (смотрите предпоследний абзац темы 1.5 и Приложение 1).

В результате получаем окончательный вариант схемы (рис.2.24).

П р и м е ч а н и я :

– в дальнейшем для достижения учебных целей мы не будем ставить нумерацию выводов корпусов микросхем, чтобы не загромождать чертежи;

– будем оставлять вспомогательные надписи, которые помогут учащимся разбираться в построении схем.

– в реальных чертежах отдельных плат или ТЭЗов (типовых элементов замены) входы и выходы оформляются иначе, чем показано на рис.2.26. Подробнее об этом будет сказано при подготовке к курсовому проектированию, а сейчас пока подписывать входы и выходы будем именно так.

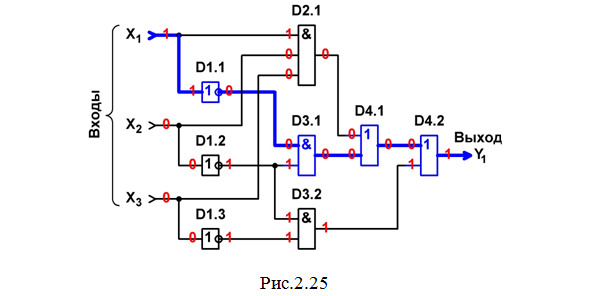

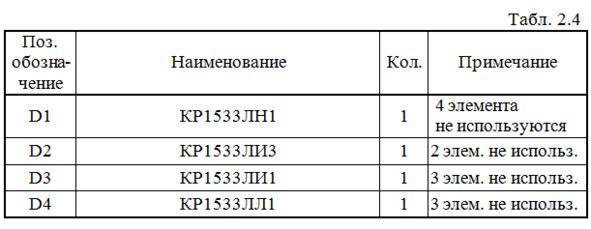

Любая реальная схема дополняется сведениями о всех используемых здесь микросхемах, любых других элементах и устройствах в виде специальной таблицы, которая имеет официальное название «Перечень элементов» (табл.2.3). По стандарту указанная таблица должна помещаться либо на поле чертежа, либо после него.

П р и м е ч а н и я к таблице:

1. Названия заголовков устанавливаются стандартом и их обязательно нужно сокращать именно так, как показано в табл.2.3.

2. Размеры таблицы также устанавливаются стандартом:

– ширина колонок по порядку слева направо: 20 (Позиционное обозначение), 110 (Наименование), 10 (Количество), 45 (Примечание) мм;

– высота строки заголовков – 15 мм;

– высота всех остальных строк – не менее 8 мм.

3. В колонке «Примечание» мы в дальнейшем будем указывать количество элементов из указанной микросхемы, которые в данной схеме использоваться не будут.

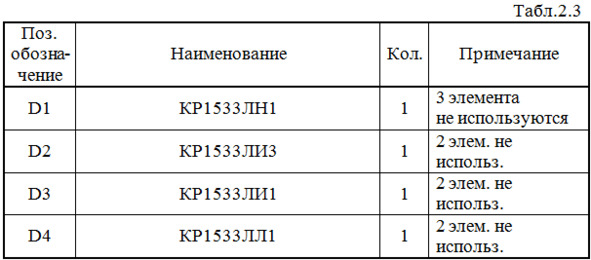

Выполним анализ работы ЦУ хотя бы в одном статическом режиме (рис.2.25). Для этого на входы подадим цифровые сигналы, например: Х1 = 1, Х2 = 0, Х3 = 0. По схеме, последовательно указывая значения сигналов на входах и выходах всех элементов (см. тему 1.2), определяем, что на выходе ЦУ формируется сигнал Y1 = 1. Сравниваем полученный результат с таблицей истинности данного ЦУ (соответствующая строка выделена красным цветом в табл.2.1) и делаем вывод: в данном случае (при заданных значениях входных сигналов) устройство сработало правильно.

На основании вышеприведенного анализа нельзя сделать вывод о правильности построения данной схемы. Такой вывод будет корректным только в том случае, если выполнить анализ работы ЦУ для всех 8 статических режимов (то есть для всех комбинаций входных сигналов) согласно таблице истинности (см. табл.2.1).

При необходимости анализ работы ЦУ в динамическом режиме производится так, как описано в теме 1.2.

Оценка качества схем в основном производится по двум параметрам: аппаратурным затратам W и задержке T.

Аппаратурные затраты W обычно определяются количеством используемых корпусов микросхем (значение ряда других параметров – потребляемой мощности, надежности и др. – допустимо считать приблизительно пропорциональными W). В данном случае мы берем:

– 3 элемента НЕ из микросхемы КР1533ЛН1, которая содержит в целом 6 элементов; то есть используем 3/6 = 0,5 корпуса ИМС;

– 1 элемент 3И из микросхемы КР1533ЛИ3 (здесь всего – 3 элемента), т.е. используем 1/3 = 0,33 корпуса ИМС;

– 2 элемента 2И из микросхемы КР1533ЛИ1, содержащей в целом 4 элемента; т.е. используем 2/4 = 0,5 корпуса ИМС;

– 2 элемента 2ИЛИ из микросхемы КР1533ЛЛ1, которая содержит всего 4 элемента; т.е. используем 2/4 = 0,5 корпуса ИМС.

Итого величина аппаратурных затрат получается равной:

W = 0,5 + 0,33 + 0,5 + 0,5 = 1,83 корпуса.

П р и м е ч а н и е: лишние элементы частично занятых корпусов микросхем не учитываются, поскольку они могут быть использованы в других узлах.

Наряду с аппаратурными затратами очень важным критерием качества схем является задержка Т. В схемах, построенных с помощью микросхем средней степени интеграции, задержка достаточно объективно оценивается средним временем задержки распространения сигнала tP (см. §1.6) входящих в нее элементов по максимально длинному пути сигналов от входа к выходу. В рамках одной серии обычно полагают, что задержка любого логического элемента равна некоторой усредненной для данной серии величине τ, которая вместе с tP непосредственно элемента включает в себя и приближенную задержку на линиях связи между элементами. Для микросхем серии КР1533 значение τ можно принять равным 8 нс.

Рассмотрим все возможные пути прохождения сигналов по схеме (рис.2.14) от входов к выходу и определим соответствующую величину задержки:

– со входа Х1 через 3 элемента – D2.1, D4.1 и D4.2, поэтому

Т = 3τ = 3·8 = 24 нс;

– со входа Х1 через 4 элемента – D1.1, D3.1, D4.1 и D4.2 (этот путь на рис.2.24 выделен жирной синей линией);

Т = 4τ = 4·8 = 32 нс;

– со входа Х2 через 3 элемента – D2.1, D4.1 и D4.2;

Т = 3τ = 3·8 = 24 нс;

– со входа Х2 через 4 элемента – D1.2, D3.1, D4.1 и D4.2;

Т = 4τ = 4·8 = 32 нс;

– со входа Х3 через 3 элемента – D2.1, D4.1 и D4.2;

Т = 3τ = 3·8 = 24 нс;

– со входа Х3 через 3 элемента – D1.3, D3.2 и D4.2;

Т = 3τ = 3·8 = 24 нс.

Таким образом, для данной схемы максимальная задержка составляет Т = 4τ = 4·8 = 32 нс.

П р и м е ч а н и е. Строго говоря, полученное численное значение (в данном случае 32 нс) особого значения не имеет, так как задержка (да и аппаратурные затраты тоже) используются в основном для сравнительной оценки качества различных вариантов схем одного и того же ЦУ. Кроме этого, схема может строиться не на микросхемах логических элементов, а включаться целиком в состав какой-либо другой микросхемы, что приведет к существенному уменьшению задержки из-за сокращения линий связи между элементами внутри микросхемы, выполненной по интегральной технологии. Поэтому в большинстве случаев достаточно оперировать величиной Т = 4τ, не указывая его численное значение.

Приведем ряд других примеров, но уже без подробных пояснений.

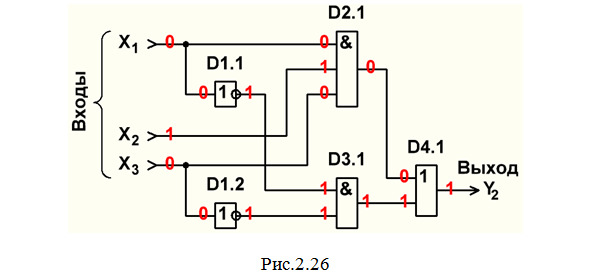

Пример 2. МДНФ (см. пример 2 из §2.2):

Y2 = X1′·X3′ \/ X1·X2·X3.

Подсчитываем требуемое количество элементов: 2 элемента НЕ +1 элемент 2И и 1 элемент 3И +1 элемент 2ИЛИ.

Подбираем микросхемы: по одной микросхеме КР1533ЛН1, КР1533ЛИ1, КР1533ЛИ3 и КР1533ЛЛ1.

Строим схему ЦУ в базисе И, ИЛИ, НЕ (рис.2.26).

Составляем перечень элементов к этой схеме (табл.2.4).

Выполним анализ работы ЦУ в статическом режиме для одной комбинации входных сигналов (см. рис.2.26 и красную строку в табл.2.2).

Определим аппаратурные затраты и задержку:

W = 2/6 + 1/3 + 1/4 + 1/4 = 0,33 + 0,33 + 0,25 + 0,25 =

= 1,16 корпуса; T = 3τ.

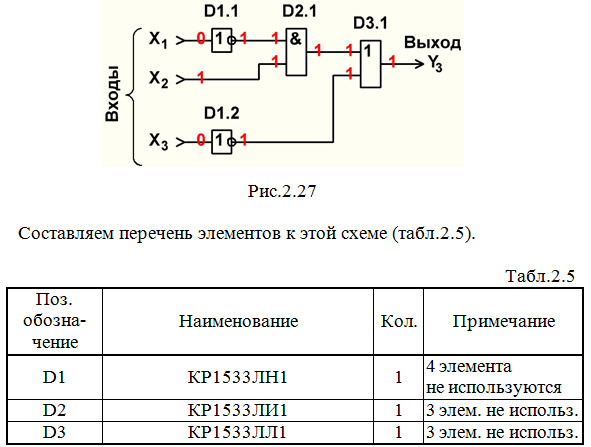

Пример 3. МДНФ (см. пример 3 из темы 2.2):

Y3 = X3′ \/ X1′·X2

Подсчитываем требуемое количество элементов: 2 элемента НЕ +1 элемент 2И +1 элемент 2ИЛИ.

Подбираем микросхемы: по одной микросхеме КР1533ЛН1, КР1533ЛИ1 и КР1533ЛЛ1.

Строим схему ЦУ в базисе И, ИЛИ, НЕ (рис.2.27).

Выполним анализ работы ЦУ в статическом режиме для одной комбинации входных сигналов (см. рис.2.27 и красную строку в табл.2.2).

Определим аппаратурные затраты и задержку:

W = 2/6 + 1/4 + 1/4 = 0,33 + 0,25 + 0,25 = 0,83 корпуса;

T = 3τ.

Рассмотрим примеры построения схем по МКНФ. Здесь первыми опять будут выполняться операции НЕ. А порядок выполнения операций логического умножения и сложения изменится, так как по законам алгебры логики (и обычной алгебры тоже) сначала должны выполняться операции в скобках – ИЛИ, а уже затем – операции И.

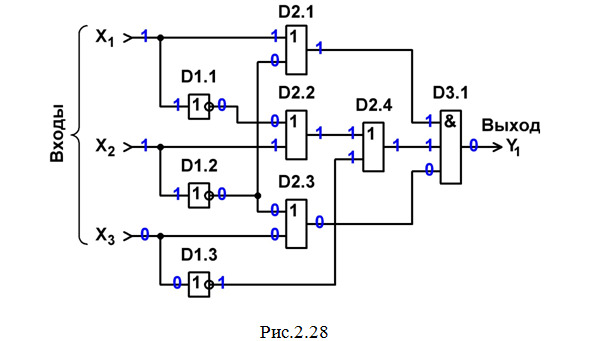

Пример 4. МКНФ (см. пример 4 из темы 2.2):

Y1 = (X1 \/ X2′) · (X2′ \/ X3) · (X1′ \/ X2 \/ X3′).

Подсчитываем требуемое количество элементов: 3 элемента НЕ +4 элемента 2ИЛИ (в третьей скобке для выполнения логического сложения трех сигналов мы вынуждены использовать 2 элемента 2ИЛИ, так как нужного здесь в принципе элемента 3ИЛИ нет в микросхемах серии КР1533) +1 элемент 3И.

Подбираем микросхемы: по одной микросхеме КР1533ЛН1, КР1533ЛЛ1 и КР1533ЛИ3.

Строим схему ЦУ в базисе И, ИЛИ, НЕ (рис.2.28).

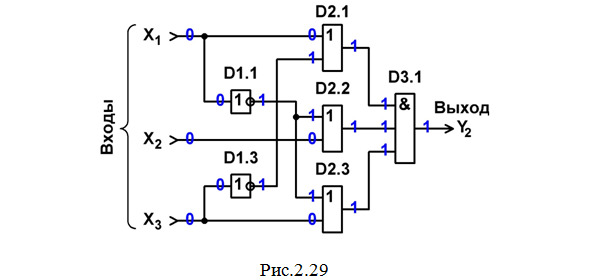

Составляем перечень элементов к этой схеме (табл.2.6).

Выполним анализ работы ЦУ в статическом режиме для одной комбинации входных сигналов (см. рис.2.28 и соответствующую синюю строку в табл.2.1).

Определим аппаратурные затраты и задержку:

W = 3/6 + 1 + 1/3 = 0,5 + 1 + 0,33 = 1,83 корпуса; T = 4τ.

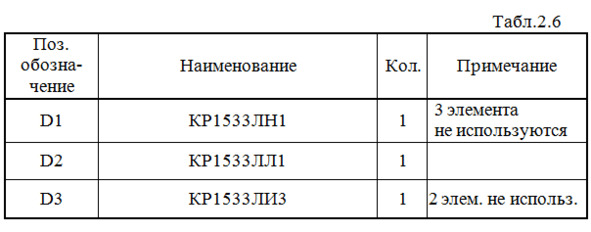

Пример 5. МКНФ (см. пример 5 из темы 2.2):

Y2 = (X1 \/ X3′) · (X1′ \/ X3) · (X1′ \/ X2).

Подсчитываем требуемое количество элементов: 2 элемента НЕ +3 элемента 2ИЛИ +1 элемент 3И.

Подбираем микросхемы: по одной микросхеме КР1533ЛН1, КР1533ЛЛ1 и КР1533ЛИ3.

Строим схему ЦУ в базисе И, ИЛИ, НЕ (рис.2.29).

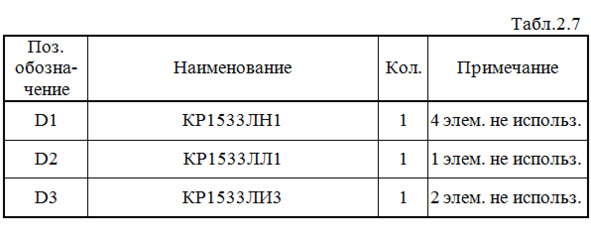

Составляем перечень элементов к этой схеме (табл.2.7).

Выполним анализ работы ЦУ в статическом режиме для одной комбинации входных сигналов (см. рис.2.29 и синюю строку в табл.2.2).

Определим аппаратурные затраты и задержку:

W = 2/6 + 3/4 + 1/3 = 0,33 + 0,75 + 0,33 = 1,41 корпуса;

T = 3τ.

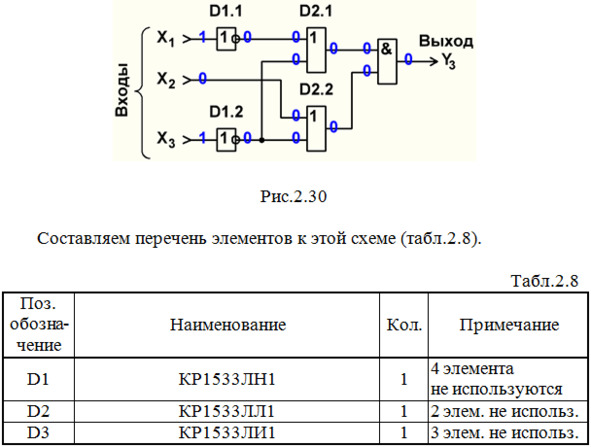

Пример 6. МКНФ (см. пример 6 из темы 2.2):

Y3 = (X2 \/ X3′) · (X1′ \/ X3′).

Подсчитываем требуемое количество элементов: 2 элемента НЕ +2 элемента 2ИЛИ +1 элемент 2И.

Подбираем микросхемы: по одной микросхеме КР1533ЛН1, КР1533ЛЛ1 и КР1533ЛИ1.

Строим схему ЦУ в базисе И, ИЛИ, НЕ (рис.2.30).

Выполним анализ работы ЦУ в статическом режиме для одной комбинации входных сигналов (см. рис.2.30 и синюю строку в табл.2.2).

Определим аппаратурные затраты и задержку:

W = 2/6 + 2/4 + 1/4 = 0,33 + 0,5 + 0,25 = 1,08 корпуса;

T = 3τ.

2.4. Переход к базису И-НЕ. Подбор микросхем, построение и анализ работы схем ЦУ в базисе И-НЕ

Значительно чаще для построения схем ЦУ используют не элементы И, ИЛИ, НЕ, а элементы И-НЕ (базис И-НЕ) или ИЛИ-НЕ (базис ИЛИ-НЕ). При этом в большинстве случаев улучшается качество схем, да и сами схемы по структуре получаются проще.

Переход к базису И-НЕ производится от МДНФ и его конечная цель заключается в следующем: следует так преобразовать МДНФ, чтобы в итоговом логическом выражении не было операций И, ИЛИ, НЕ, а были бы только операции И-НЕ.

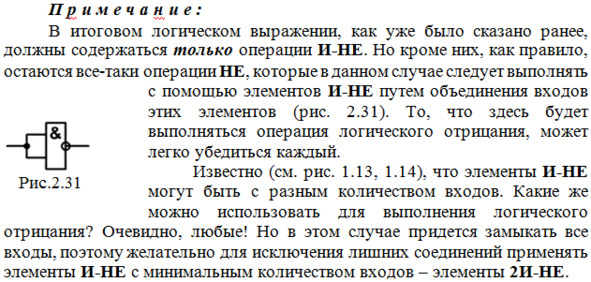

Переход выполняется в следующем порядке (под буквами А, B, C, D и т. д. понимаются логические сигналы 0 или 1, а также любые логические операции и выражения, дающие в результате опять же сигналы 0 или 1):

1. Используется закон двойного отрицания (двойной инверсии):

A = A′′.

Справедливость этого закона проверить несложно, если вместо А подставить 0 или 1.

2. Применяется первая форма закона де Моргана:

(B \/ C \/ D \/ …)′ = B′·C′·D′·…

Правильность и этого закона тоже проверить несложно, если вместо В, С, D и т. д. подставить любую комбинацию сигналов 0 и 1.

3. Полученное логическое выражение рекомендуется записать с использованием символа «штрих Шеффера» (смотрите табл.1.1), например:

(X1·X2)′ = X1 / X2.

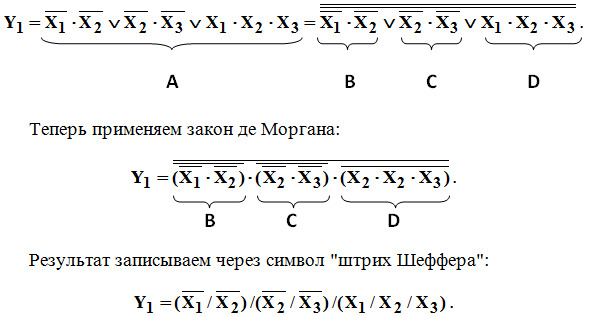

Пример 1. МДНФ (см. пример 1 из темы 2.2):

Y1 = X1′·X2′ \/ X2′·X3′ \/ X1·X2·X3.

Переходим к базису И-НЕ. Для этого сначала используем закон двойного отрицания:

Определяем требуемое количество элементов с учетом нужного количества входов у каждого элемента:

– для выполнения операций логического отрицания сигналов X1, X2 и X3 берем три элемента 2И-НЕ (смотрите П р и м е ч а н и е выше);

– чтобы выполнить операцию в первой скобке, следует использовать элемент 2И-НЕ, так как в данной операции участвуют два сигнала: X1′ и X2′;

– для реализации операции во второй скобке нужен элемент 2И-НЕ, потому что здесь в операции тоже участвуют два сигнала: X2′ и X3′;

– чтобы выполнить операцию в третьей скобке, придется взять элемент 3И-НЕ, так как в данной операции участвуют три сигнала: X1, X2 и X3;

– и последним мы должны поставить элемент 3И-НЕ, потому что на его входы будут поступать три сигнала, являющиеся результатами операций в трех скобках.

Всего в схеме ЦУ: 5 элементов 2И-НЕ (напомним, что из них – три элемента для выполнения логического отрицания!) +2 элемента 3И-НЕ.

Подбираем микросхемы. Элементы 2И-НЕ имеются в составе микросхемы КР1533ЛА3 (см. рис. 1.13), содержащей 4 элемента 2И-НЕ; так как нам требуется 5 таких элементов, то придется взять две микросхемы КР1533ЛА3, причем в одной из них три элемента использоваться не будут. Элементы 3И-НЕ входят в состав микросхемы КР1533ЛА4 (см. рис. 1.14), содержащей 3 элемента 3И-НЕ; нам нужны два элемента, поэтому достаточно использовать одну микросхему КР1533ЛА4, причем один элемент данной ИМС оказывается лишним.

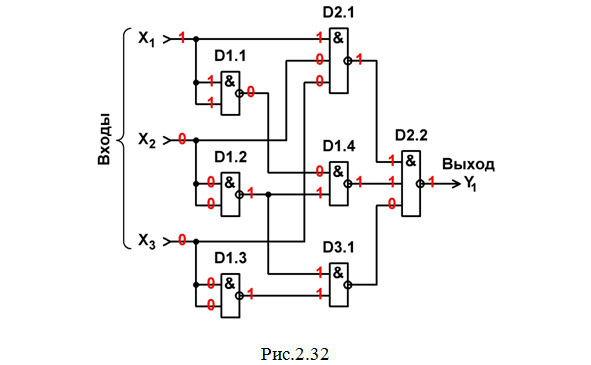

Строим схему ЦУ в базисе И-НЕ (рис. 2.32).

На этом же рис.2.32 выполнен анализ работы схемы ЦУ в статическом режиме для одной комбинации входных сигналов (см. красную строку в табл. 2.1).

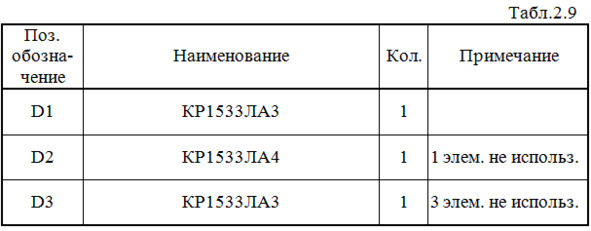

Составляем перечень элементов к этой схеме (табл.2.9).

Определим аппаратурные затраты и задержку:

W = 1 + 2/3 + 1/4 = 1 + 0,67 + 0,25 = 1,92 корпуса; T = 3τ.

Пример 2. МДНФ (см. пример 2 из темы 2.2):

Y2 = X1′·X3′ \/ X1·X2·X3.

Переходим к базису И-НЕ: