Полная версия

Частотный синтез на основе ФАПЧ. Обзор методов синтеза

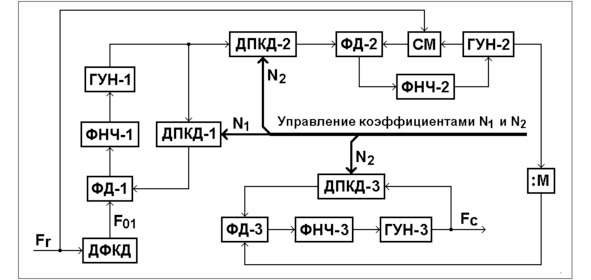

FC=FКС±FМС=N2F02±N1F01/M

Генераторы, выходной (ГУН) и крупной сетки (ГУН-2) имеют практически одинаковый частотный диапазон перестройки, поскольку FС>> FМС, то есть диапазоны отличаются лишь на небольшую величину FМС. Поэтому необходимо тщательно их сопрягать по управляющим напряжениям, чтобы избежать «зеркальной» настройки выходного генератора.

В синтезаторах по такой структуре выходной уровень шума определяется в полосе суммирующего кольца генератором ГУН-2, а за полосой – выходным генератором ГУН.

В качестве примера положим, что требуется получить диапазон частот от 700 МГц до 1 ГГц с шагом dF=10 кГц. Тогда можно выбрать следующие параметры петель ФАПЧ: F01=F02=1 МГц; изменение коэффициента N1 – от 900 до 1000 через единицу; диапазон перестройки ГУН-1 от 900 МГц до 1 ГГц и M=100, то есть диапазон частот FМС на входе суммирующей петли равен FМС=9÷10 МГц с шагом 10 кГц; изменение коэффициента N2 второй петли – от 691 до 990 через единицу; диапазон перестройки генератора ГУН-2 – от 691 до 990 МГц с шагом 1 МГц.

Выбор такой довольно высокой частоты сравнения в фазовых детекторах, как 1 МГц, позволяет обеспечить в трёхпетлевом синтезаторе время переключения частоты порядка долей миллисекунд при высокой спектральной чистоте выходного сигнала.

Недостаток – очевидная сложность системы, необходимость тщательной проработки конструкции с экранированием отдельных узлов, чтобы избежать в спектре сигнала помех комбинационного характера.

1.7. Схема Сровера

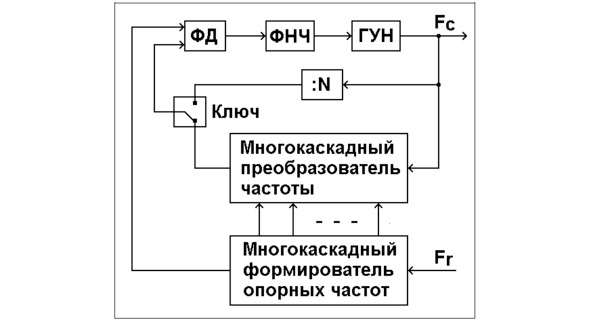

Разновидностью трёхпетлевого синтезатора является вариант, предложенный Сровером [26]. Он показан на рисунке 7. В нём используются два синхронно управляемых делителя с одинаковыми коэффициентами деления при последовательном соединении петель ФАПЧ. В некоторых периодических изданиях эта схема получила название «близнецы».

Рис.7. Схема Сровера

В первой петле представленной схемы формируется исходный шаг сетки частот, в третьей – крупная сетка с шагом Fr/M, вторая петля выполняет функцию суммирования, но в отличие от суммирующей петли предыдущей схемы здесь требования к петле значительно слабее, поскольку она выполняет сложение практически на одной частоте Fr. Наличие делителя с коэффициентом деления M и малая перестройка ГУН-2 снижают требования по шумам к генераторам первой и второй петель. Выходной уровень шума в этой схеме определяется, в первую очередь, генератором ГУН-3.

Согласно со структурой схемы выходная частота Fc синтезатора определяется выражением

FC= (N1F01+N2Fr) /M.

Аналогично предыдущей схеме данная структура позволяет выбирать повышенные частоты сравнения в петлях, что позволяет реализовать синтезатор с улучшенными характеристиками спектральной чистоты и быстродействия.

Недостатки трехпетлевых вариантов построения синтезаторов вполне очевидны:

– значительное увеличение габаритов, потребления электроэнергии и стоимости в сравнении с однопетлевым синтезатором;

– наличие трех высокочастотных генераторов является, как правило, причиной образования паразитных дискретных составляющих в спектре сигнала синтезатора, для устранения которых требуются дополнительные усилия схемно-конструктивного плана.

2. Комбинированные схемы

2.1. Схема QuickSyn

Идея частотного синтеза, предложенная Александром Ченакиным. раскрыта в его американском патенте [27] и описана в ряде публикаций, например [28÷30]. Здесь мы ограничимся лишь описанием упрощённой схемы, только чтобы пояснить саму идею, особо не углубляясь в подробности.

Схема показана на рисунке 8. Она представляет собой систему фазовой автоподстройки частоты, содержащую в своей основе, как обычно, фазовый детектор ФД, фильтр нижних частот ФНЧ и генератор, управляемый напряжением ГУН. Особенность синтезатора заключается в построении цепи обратной связи системы.

Рис.8. Схема QuickSyn

Эта цепь содержит два параллельных тракта, работающих последовательно во времени и образующих две петли ФАПЧ. При задании нового значения синтезируемой частоты, ключ переходит в соответствующее положение, чтобы сработала первая петля (та, в которой включён делитель частоты с переменным коэффициентом деления N) и привела частоту сигнала к заданному значению с точностью, достаточной для захвата частоты второй петлёй.

После этого включается в работу вторая петля. Она действует через многокаскадный преобразователь частоты в цепи обратной связи. Преобразователь частоты содержит последовательно включённые смесители частоты, в которых в результате взаимодействия с опорными частотами происходит смещение частоты сигнала вниз к частоте сравнения в ФД. Опорная частота для каждого последующего каскада понижается с помощью многокаскадного формирователя опорных частот, состоящего из набора делителей, умножителей и смесителей частоты. Этот блок работает от сравнительно высокочастотного опорного источника частоты Fr. Здесь, можно сказать, просматривается аналогия с обычным аналоговым синтезатором с той лишь разницей, что преобразование частоты происходит вниз, а не вверх. Выход последнего каскада формирователя опорных частот служит также опорой для обеих петель ФАПЧ.

Задача для преобразователя частоты – донести спектр управляемого генератора до ФД без деления частоты. Благодаря этому, не снижается усиление в этой петле, как это имеет место в предыдущей петле, и этим достигается высокая эффективность подавления собственных шумов управляемого генератора.

Важно отметить, что интермодуляционные продукты такого многоступенчатого преобразователя частоты являются гармониками частоты сравнения фазового детектора и могут быть легко подавлены фильтром ФАПЧ. Таким образом, предложенное архитектурное решение позволяет получить довольно низкие побочные составляющие (спуры) в сравнении с классическими схемами.

Однако отмеченное достоинство схемы реализуется лишь при достаточно крупной сетке частот, шаг которой равен частоте сравнения в ФД. При уменьшении шага сетки уменьшается и частота сравнения, сужается полоса петли и соответственно снижаются качество спектра сигнала и быстродействие синтезатора.

Описанную схему можно использовать как составную часть более сложной структуры, дополнительно включающей средства для заполнения крупной сетки более мелкой сеткой. Например, можно добавить ещё одну петлю ФАПЧ, чтобы просуммировать полученную крупную сетку с мелкой, образованной с помощью DDS синтезатора.. При этом, конечно, необходимо принять меры для обеспечения достаточно низкого уровня помех от DDS. К этим мерам можно отнести использование нескольких опорных частот при выборе диапазона DDS с относительно малым уровнем помех, скажем порядка -75 дБн, подъём этого диапазона вверх с последующим делением частоты, что соответственно даёт дополнительное улучшение спектра. Более простым вариантом может оказаться также реализация опорного сигнала Fr в относительно узкой полосе частот (достаточной для заполнения крупной сетки) с помощью дополнительной петли ФАПЧ.

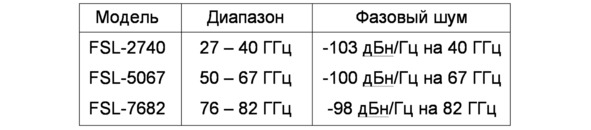

В итоге общая структура синтезатора существенно усложняется. Она реализована на практике в линейке синтезаторов типа QuickSyn фирмы Phase Matrix, ныне в составе National Instruments (см. те же, приведенные выше ссылки на источники), где показала очень высокие характеристики спектральной чистоты. В модели QuickSyn Lite FSW-0010, обеспечивающей диапазон от 0,5 до 10 ГГц, «полка» шума на частоте сигнала порядка 10 ГГц в полосе ФАПЧ составляет около -120 дБн/Гц, а уровень дискретных компонентов менее -70 дБн и время переключения порядка десятков микросекунд. В следующей модели – FSW-0020 – диапазон частот расширен до 20 ГГц, и на её базе создан ряд синтезаторов миллиметрового диапазона, характеристики которых приведены в Табл.3. При этом во всех приведенных модификациях шаг сетки частот равен 1 Гц, паразитные спектральные составляющие не превышают -60 дБн и время переключения частоты не более 1 мс.

Таблица 3

Недостаток – сравнительно высокая сложность и, соответственно, – стоимость. Вместе с тем всё относительно. Если при этом учесть довольно высокое отношение качества к сложности и цене, то вряд ли это можно отнести к недостаткам. Более того, полученные характеристики спектральной чистоты и быстродействия – это не архитектурные ограничения в принципе, а конкретная и весьма упрощенная реализация. Эти характеристики могут быть значительно улучшены при более полном задействовании потенциальных возможностей данного метода синтеза.

2.2. Схема на серийных микросхемах

Конечно, не всем заказчикам нужны ультранизкие шумы и спуры, а также и экстра высокое быстродействие, что в сумме достигается, как правило, за счёт увеличения энергопотребления, габаритов и стоимости. Поэтому существует задача разработки такого прибора, в котором характеристики в первой названной группе требований могут быть несколько ослабленными, зато во второй – значительно ужесточены. Один из вариантов решения этой задачи представлен в работах [31÷33].

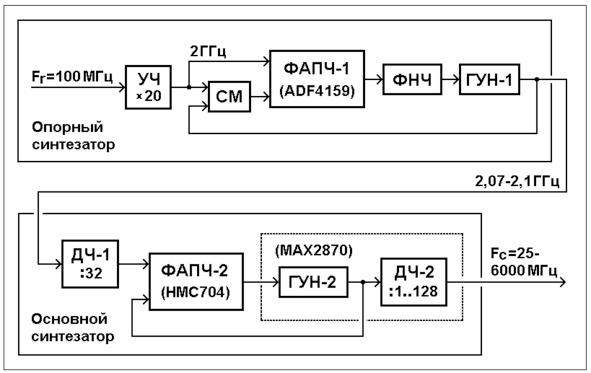

Предложенная схема синтезатора поясняется рисунком 9, который иллюстрирует пример получения из опорной частоты Fr=100МГц, умноженной в 20 раз, сигнала с частотой Fc в диапазоне от 25 до 6000 МГц.

Рис.9. Схема синтезатора на серийных микросхемах

Синтезатор состоит из двух последовательно включённых блоков – опорного и основного синтезаторов. Первый и из них обеспечивает частоту с малым шагом перестройки в сравнительно небольшом диапазоне, а второй – использует эту частоту в качестве опорной, расширяя диапазон перестройки синтезатора в целом до нескольких октав. Частотные преобразования, как и обозначения элементов на схеме, пояснений не требуют.

Собственно, это известный принцип построения синтезатора, который, в частности, использован и в QuickSyn (см. предыдущий раздел). Новизна состоит в удачном подборе микросхем для названных блоков.

Например, вместо DDS для получения мелкой сетки в опорном синтезаторе, как это имеет место в том же QuickSyn, здесь используется дробный делитель частоты с дельта-сигма модулятором. Для этого подходит, например, микросхема ADF4159 от Analog Devices. Это существенно экономит энергопотребление и габариты, так как делитель частоты находится в составе микросхемы (ФАПЧ-1), где содержатся и другие необходимые узлы: частотно-фазовый детектор, токовый ключ и др. Фактически, система потребляет столько, сколько она потребляла бы без прямого цифрового синтезатора (экономия порядка 0,5÷1 Вт). Уровень остальных характеристик не сильно уступает решению с DDS.

Так же и в блоке основного синтезатора могут быть использованы экономичные недорогие серийные микросхемы: HMC704 от Hittite (ФАПЧ-2) и MAX2870 от Maxim Integrated (ГУН-2 и ДЧ-2).

По описанной структуре в ЗАО НПФ «Микран» разработан портативный USB синтезатор PLG06 [34] со следующими основными характеристиками: диапазон выходных частот 25—6000 МГц с шагом 1 Гц; уровень фазовых шумов -122 дБн/Гц при отстройке 10 кГц от несущей 1 ГГц; уровень негармонических составляющих в спектре -70 дБн; уровень гармоник -30 дБн; время перестройки частоты 100 мкс.

Имеется режим аналоговой модуляции: АМ, ФМ, ЧМ, ИМ (внешний/внутренний источник) и режим сканирования.

Прибор, обладая функциональными возможностями классических лабораторных генераторов, потребляет всего 2,5 Вт, питается и управляется через один провод USB 2.0. Габариты прибора всего лишь 125х65х25 мм.

2.3. DDS в петле ФАПЧ

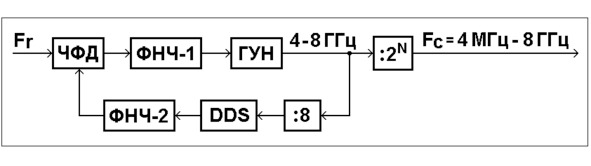

Идею использования DDS в петле ФАПЧ для формирования сетки частот рассмотрим на примере генератора SG8-HP01M фирмы ООО Адвантех, Москва [36]. Схема генератора показана на рисунке 10.

Рис.10. Пример синтезатора с DDS в петле ФАПЧ

DDS в этой схеме выполняет роль делителя частоты с переменным коэффициентом деления (ДПКД). Он тактируется поделённой в 8 раз частотой в октавном диапазоне 4÷8 ГГц, поступающей от ГУН. Коэффициент деления DDS, как делителя частоты, также перестраивается в октавном диапазоне в соответствии с октавным частотным диапазоном 0,5÷1 ГГц на его входе. Таким образом, частота на выходе DDS остаётся постоянной и равной опорной частоте Fr (при наличии синхронизма в петле).

Верхний, наиболее крупный, октавный диапазон получается непосредственно на выходе ГУН, а остальные, более мелкие, – после деления верхнего диапазона двоичными делителями частоты, как это будет рассмотрено в разделе 2.5.

Очевидное достоинство схемы, как и любой другой однопетлевой структуры, состоит в простоте её реализации. Недостаток – довольно высокий уровень негармонических составляющих в спектре сигнала, происходящих из DDS.. При постоянном значении опорной частоты Fr он достигает -50 дБн в полосе отстроек от сигнала 2 МГц. Этот уровень можно снизить на 10 дБ путём использования двух опорных частот, переключаемых автоматически по встроенной программе.

В рассматриваемом генераторе уровень фазовых шумов составляет -120 дБн на частоте сигнала 1 ГГц при отстройке на 10 кГц и время переключения частот – порядка 4 мс. Полученные характеристики можно считать достаточными, чтобы данный отечественный прибор мог составить конкуренцию зарубежным аналогам.

2.4. Схема Садовского

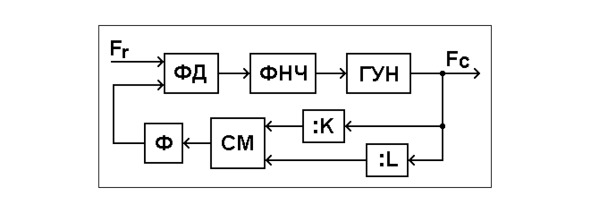

Идея, предложенная автором, отличается особым способом построением ДДПКД в петле ФАПЧ [37]. Схема синтезатора частоты, в которой используется эта идея, показана на рисунке 11.

Рис.11. Схема Садовского

Дробный делитель частоты представлен в ней двумя делителями с целочисленными коэффициентами K и L и смесителем частоты СМ с фильтром Ф на его выходе. Результирующий коэффициент деления для такой структуры равен

N=KL/ (K±L)

.где К больше L.

Достоинство идеи состоит в том, что такой делитель частоты, обладая свойствами дробного деления, не имеет на своём выходе помех дробности. Это можно показать на примере.

Положим, что при опорной частоте Fr=10 МГц требуется получить частоту Fc=119 МГц на выходе ГУН, включенного в петлю ФАПЧ. При этом необходимо иметь коэффициент деления в петле равный N=11,9. Его можно обеспечить, задав следующие значения коэффициентов деления: K=17 и L=7. Тогда частоты на входах смесителя СМ окажутся равными соответственно FK=119/17=7 МГц и FL=119/7=17 МГц, а их разность на выходе смесителя составит 10 МГц, которая и используется для сравнения с опорой частотой 10 МГц в фазовом детекторе ФД.

Если же использовать суммирование частот FK и FL при тех же коэффициентах деления 17 и 7, то получится результирующий коэффициент деления

N= (17×7) / (17+7) =4.9583 (3)

и соответствующая ему частота равна Fc=49,583 (3) МГц. При этом частоты на выходах соответствующих делителей равны FK=2,916 (6) МГц и FL=7,083 (3) МГц, а их сумма равна 10 МГц, которая, как и в предыдущем случае, используется для сравнения в фазовом детекторе.

Недостатком рассмотренной структуры является необходимость включения фильтра Ф, чтобы избавиться от комбинаций типа +/-nFK+/-mFL. Это существенно ограничивает возможности широкого выбора коэффициентов K и L. Кроме того, стремление обеспечить высокое разрешение по частоте приводит к необходимости соответствующего увеличения этих коэффициентов и сужения полосы пропускания фильтра, что – и то и другое – соответственно снижает быстродействие синтезатора. К недостаткам можно также отнести и относительно сложный алгоритм выбора требуемой частоты сигнала. Для каждых конкретных требований к диапазону частот синтезатора, шагу сетки частот и быстродействию необходима таблица с предварительно рассчитанными значениями коэффициентов K и L.

Однако, благодаря бесспорным достоинствам схемы по сравнению со схемами, использующими как целочисленные, так дробные коэффициенты деления, данная схема могла бы найти практическое применение, хотя и ограниченное отмеченными недостатками. Более обстоятельно схема проанализирована в работе [38].

2.5. Расширение диапазона частот

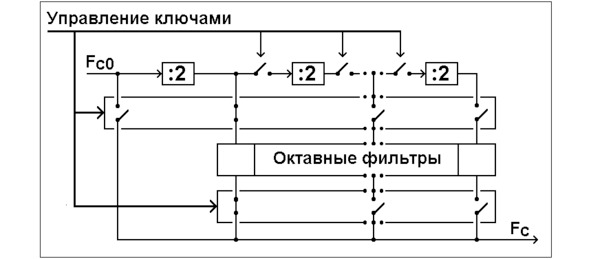

Понятно, что пределы перестройки ГУН ограничены, и в первую очередь из-за необходимости обеспечения допустимого уровня шума. Генераторы с перекрытием по частоте более октавы практически не применяются. Расширить диапазон частот синтезатора можно, используя набор из нескольких коммутируемых генераторов. Однако это довольно сложно и дорого. Но если уже получен октавный диапазон, то далее можно расширять диапазон частот синтезатора вниз по частоте достаточно простым способом, как это показано на рисунке 12.

Рис.12. Схема расширения диапазона частот Fc

На рисунке показан пример получения диапазона частот Fc=FС0/2, где FС0 – исходный октавный диапазон. Чтобы избежать попадания в спектр сигнала Fc её субгармоник, последующие делители частоты, после используемых, отключаются. В качестве делителей частоты целесообразно использовать триггеры с выходным напряжением в виде меандра, не содержащим второй гармоники. Поэтому синусоидальный сигнал на выходе Fc может быть получен с помощью довольно простых фильтров нижних частот октавного диапазона.

Данный способ расширения диапазона частот широко используется на практике [39], в частности в разработках фирм Phase Matrix / NI, США, (FSW-0010), Stanford Research Systems, США (7SG392, 7SG394, 7SG396), AnaPico Inc, Швейцария (APSIN6010), Advantex, Москва (SG8), Микран, Томск (PLG06) и некоторых других фирм.

3. Схемы с дробным делителем частоты и компенсацией помех дробности и другие схемы

Перейдём далее к рассмотрению однопетлевых структур с дробным делителем частоты и различными вариантами схем для компенсации помех дробности.

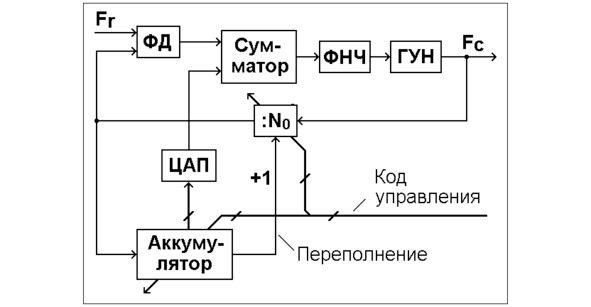

3.1. Схема Бреймера-Джиллета

Один из таких вариантов представлен на рисунке 13. Если в общих чертах, то она почти одновременно запатентована авторами Бреймером и Джиллетом [40, 41]. Правда, в описаниях к их патентам много внимания уделено построению оригинальных схем ДДПКД, хотя это не касается самого принципа компенсации помех дробности и потому не отражено на приведенном рисунке.

Рис.13. Схема Бреймера-Джиллета

ДДПКД представлен в виде целочисленной части с коэффициентом деления N0 и дробной части, выполненной на аккумуляторе (накапливающем сумматоре). Импульс переполнения последнего передаётся в целочисленную часть, и общий коэффициент деления увеличивается при этом на единицу, из-за чего и возникает помеха дробности.

Для её компенсации используется ЦАП, с помощью которого формируется сигнал – копия помехи, продетектированной в ФД. В сумматоре напряжения с выходов ЦАП и ФД складываются в противофазе, благодаря чему помеха дробности подавляется.

Понятно, что степень подавления помехи зависит от точности ЦАП и от точности сумматора, и эти точности, естественно, ограничены. Поэтому если ёмкость аккумулятора довольно большая (чтобы получить достаточно мелкий шаг сетки частот), нет смысла брать ЦАП той же ёмкости, её ограничивают 12÷14 разрядами, подключаемым к соответствующим старшим разрядам аккумулятора.

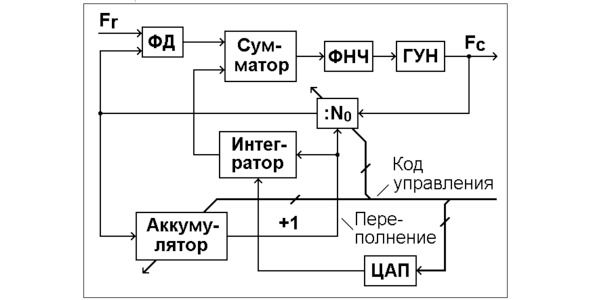

3.2. Вариант с интегратором

Другой вариант [42] схемы компенсации помехи дробности показан на рисунке 14. В нём используются, в основном, те же блоки, что и в предыдущей схеме. Добавлен только интегратор, а ЦАП предназначен для другой цели.

Рис.14. Вариант схемы с интегратором

Каждое переполнение аккумулятора вызывает скачёк частоты на выходе делителя частоты. Чтобы его скомпенсировать, необходимо создать сигнал, соответствующий получаемому при этом отклонению фазы, и сложить его в противофазе с напряжением на выходе фазового детектора. Для этого и служит интегратор. Он может быть выполнен на базе операционного усилителя.

Требуемый уровень компенсирующего сигнала обратно пропорционален коэффициенту деления. Поэтому при достаточно большом частотном перекрытии синтезатора, и, следовательно, широком диапазоне изменений коэффициента деления, необходимо управлять коэффициентом передачи интегратора, для чего и служит ЦАП. Он может быть использован в качестве источника для питания интегратора, чтобы напряжение на его выходе контролировалось управляющим кодом. В предыдущей схеме такая возможность отсутствовала. Но и там можно ввести дополнительный ЦАП, питающий уже имеющийся (который должен быть умножающего типа) и подключенный к управляющей шине.

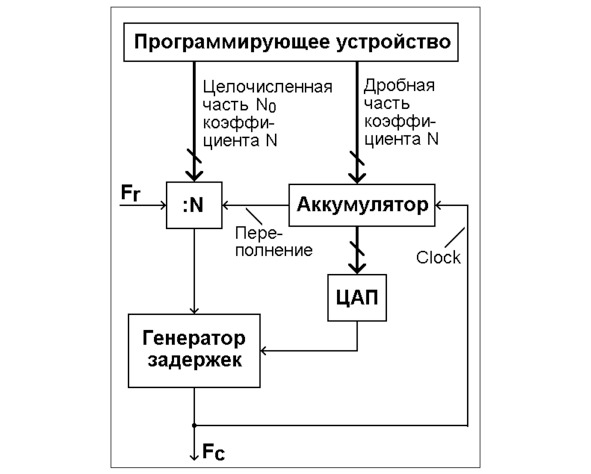

3.3. Схема Кокса

По своей структуре схему Кокса [43] можно отнести к прямым цифровым синтезаторам с некоторыми особенностями. Сигнал в ней получается делением опорной частоты в переменное дробное число раз с последующей компенсацией помех дробности путём программируемого временного сдвига сигнала на выходе схемы.

Схема представлена на рисунке 15. Она содержит программирующее устройство для задания целочисленной и дробной частей коэффициента N, поглощающий счётчик (обозначен на схеме как: N), аккумулятор для формирования дробной части коэффициента деления и генератор задержек, управляемый цифро-аналоговым преобразователем (ЦАП). Поглощающий счётчик тактируется импульсами опорной частоты Fr, а аккумулятор – сигнальными импульсами частоты Fc. Поглощающий счётчик вместе с аккумулятором образуют, в целом, схему ДДПКД.

Рис.15. Схема Кокса

Работу схемы можно рассмотреть на конкретном примере. Положим, что при опорной частоте, равной Fr=100 МГц, требуется получить частоту сигнала Fc=30 МГц. Это значит, что при некотором разрешении по частоте импульс на выходе синтезатора должен появляться через каждые 3,3333 периодов опорных импульсов. Для этого целочисленная часть коэффициента деления N устанавливается равной N0=3, а для обеспечения дробной части этого коэффициента, число на входе аккумулятора равно 3333 при его ёмкости, равной 10000. Понятно, что при этом искомая частота 30 МГц будет получена с погрешностью 300 Гц. Положим также, что поглощающий счётчик и аккумулятор оба включаются в работу при нулевых начальных условиях.

Поглощающий счётчик устроен таким образом, что импульсом переполнения аккумулятора один опорный импульс с его входа вычёркивается.

Первые три опорных импульса беспрепятственно проходят через поглощающий счётчик, создавая первый сигнальный импульс, который и далее беспрепятственно проходит через генератор задержек на выход схемы. Это потому, что, во-первых, импульс переполнения аккумулятора отсутствует, а во-вторых, содержимое аккумулятора, как и ЦАП, равно нулю и, следовательно, генератор задержек не создаёт временного сдвига для этого импульса. Данный импульс, воздействуя на аккумулятор, меняет его содержимое с нуля до 3333.

Следующие 3 опорных импульса также беспрепятственно проходят через поглощающий счётчик, создавая на его выходе второй сигнальный импульс. Однако далее этот импульс проходит на выход схемы с задержкой на 0,3333 периода Tr опорных импульсов, которая создаётся генератором задержек под воздействием сигнала с выхода ЦАП. Этот сигнальный импульс увеличивает содержимое аккумулятора до значения 6666.

После трёх последующих импульсов Fr получается третий сигнальный импульс на выходе поглощающего счётчика, который проходит на выход схемы с задержкой 0,6666Tr в соответствии с новым значением содержимого аккумулятора. Аналогичным образом формируется четвёртый сигнальный импульс с задержкой 0,9999Tr.

На пятом сигнальном импульсе аккумулятор переполняется, его содержимое сбрасывается до значения 3332, а его импульсом переполнения вычёркивается один импульс Fr на входе поглощающего счётчика. И далее схема действует по описанному алгоритму, выравнивая, с помощью генератора задержек, расстановку сигнальных импульсов во времени, чтобы сделать процесс периодическим, то есть исключить помеху дробности.